-

SPICE Model

SPICE ModelBaseband Modeling

• BSIMProPlus

RF Modeling

• MeQLab

Model Extraction Automation

• SDEP

Model QA

• ME-Pro

-

PDK

PDKPCell Development

• PCellLab

PDK Verification

• PQLab

-

Standard Cell

Standard CellLibrary Characterization

• NanoCell

Library Validation

• LibWiz

-

Fabrication

FabricationLithography Modeling and Simulation

• FabLitho

Reticle Automated Design

• FAR

-

Design Environment

Design EnvironmentSchematic Capture

• NanoDesigner SE

Layout Editor

• NanoDesigner LS

Interactive Physical Verification

• NanoDesigner iV

Design Optimization

• NanoDesigner Optimizer

-

Circuit Simulation

Circuit SimulationSPICE Simulator

• NanoSpice • NanoSpice X • NanoSpice Giga

FastSPICE Simulator

• NanoSpice Pro • NanoSpice Pro X

Mixed Signal

• NanoSpice MS

Waveform Analysis

• NanoWave

-

Circuit Analysis

Circuit AnalysisStatic and Dynamic Circuit Check

• NanoSpice CCK

Yield Analysis

• NanoYield

Signal Integrity

• NanoSpice SI

Critical Path Analysis

• PathInspector

Power Device Design Verification

• PTM

Power Distribution Network Analysis

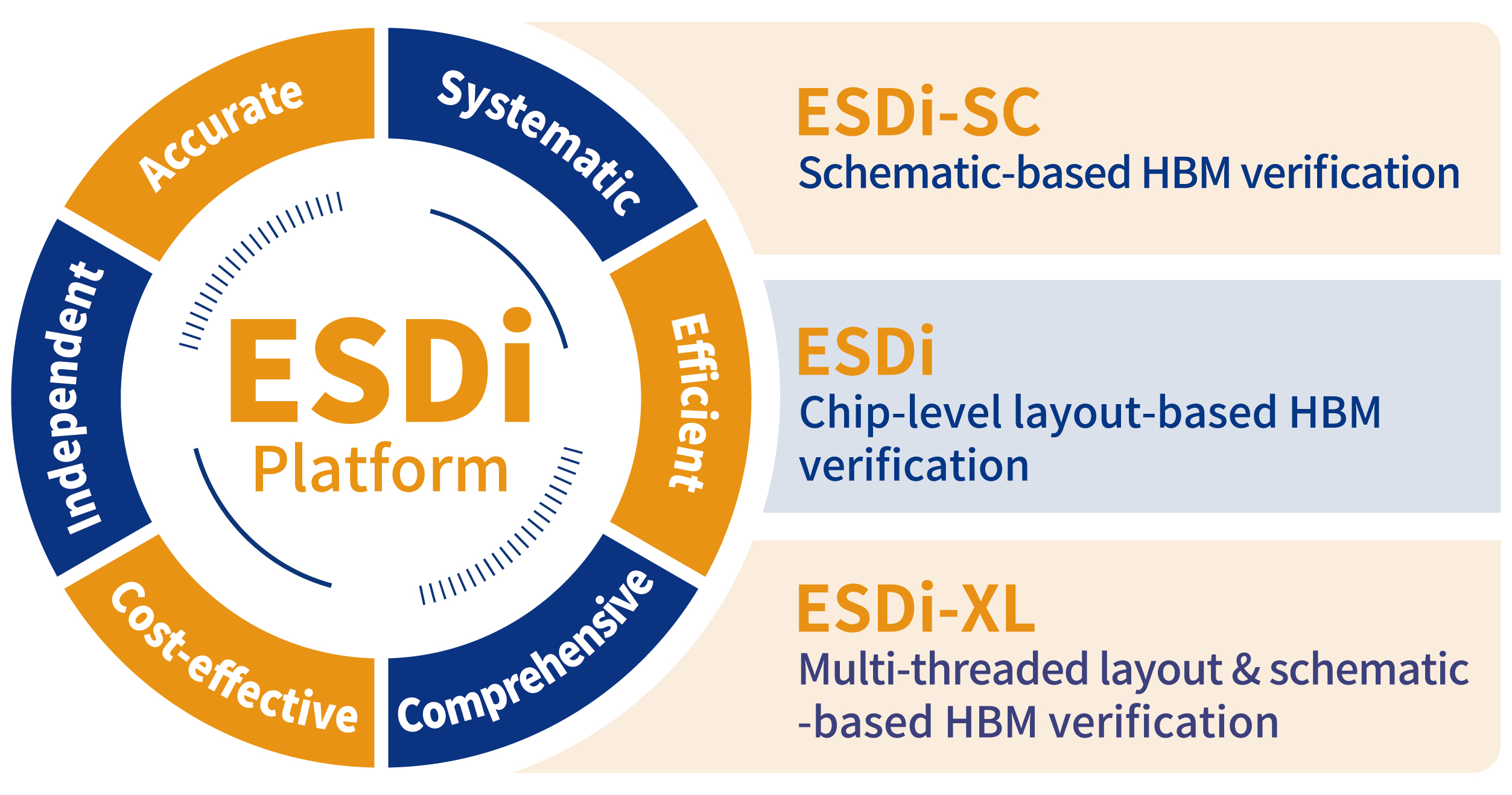

ESD Verification

• ESDi

-

Circuit Simulation

Circuit SimulationDigital Simulation

• VeriSim

-

Standard Cell

Standard CellLibrary Characterization

• NanoCell

Library Validation

• LibWiz

-

Design & Verification

Design & VerificationTiming Analysis

• TRASTA

Floor Planning

• NavisPro

Signal Integrity Analysis

• NanoSpice SI

Power Design Analysis

• PTM

ESD Verification

• ESDi

Chip-to-Package Connectivity Verification

• PadInspector

-

Parametric Testing

Parametric TestingSemiconductor Parametric Analyzer

• FS-Pro • FS800

-

Noise Measurement

Noise MeasurementLow Frequency Noise

• 9812DX • 9812E • 9812HF

AC Dynamic Noise

• 9812AC

-

Integrated Testing

Integrated Testing

Electrical Parameter Testing Software

• LabExpress

-

Benchtop Instrument

Benchtop InstrumentSource Measure Unit

• P1800